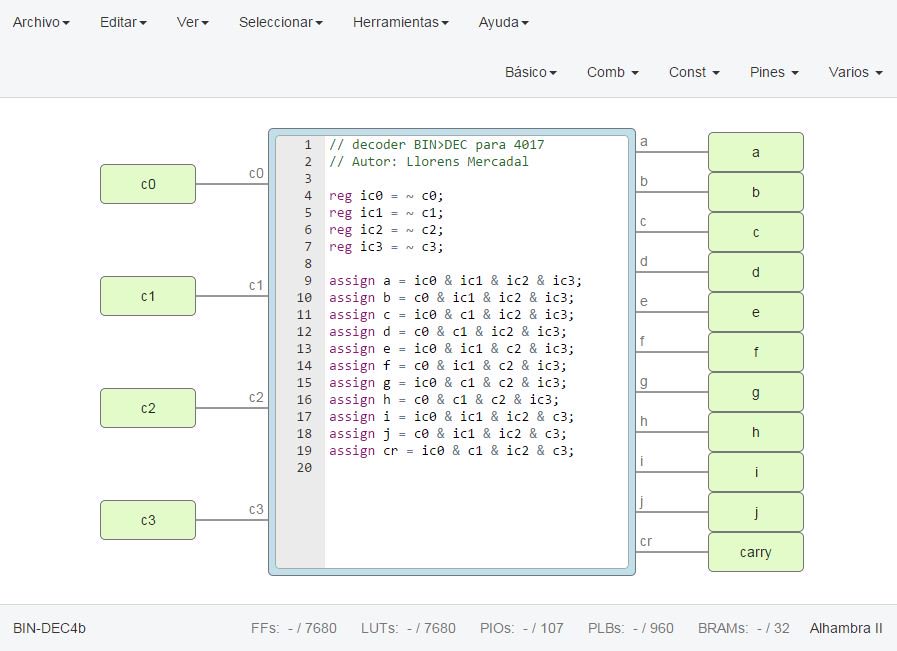

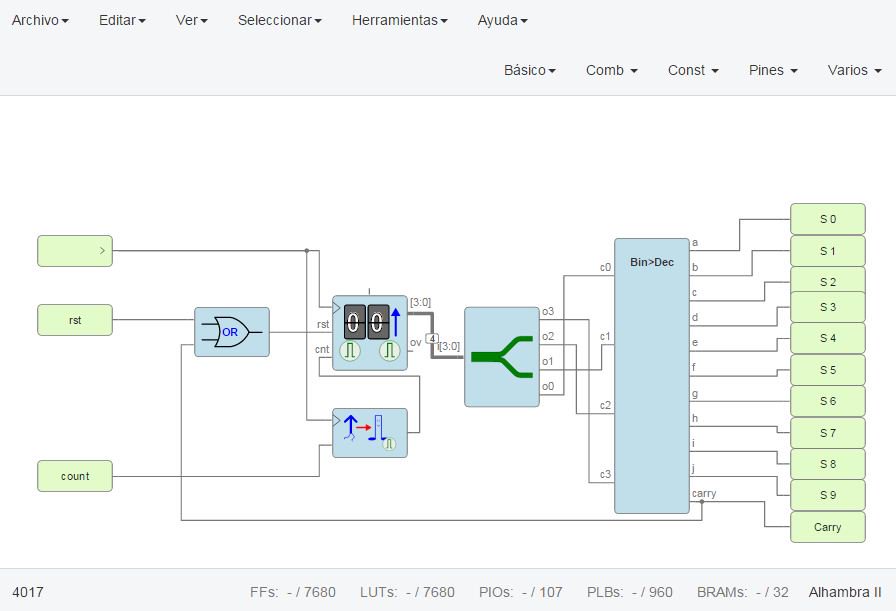

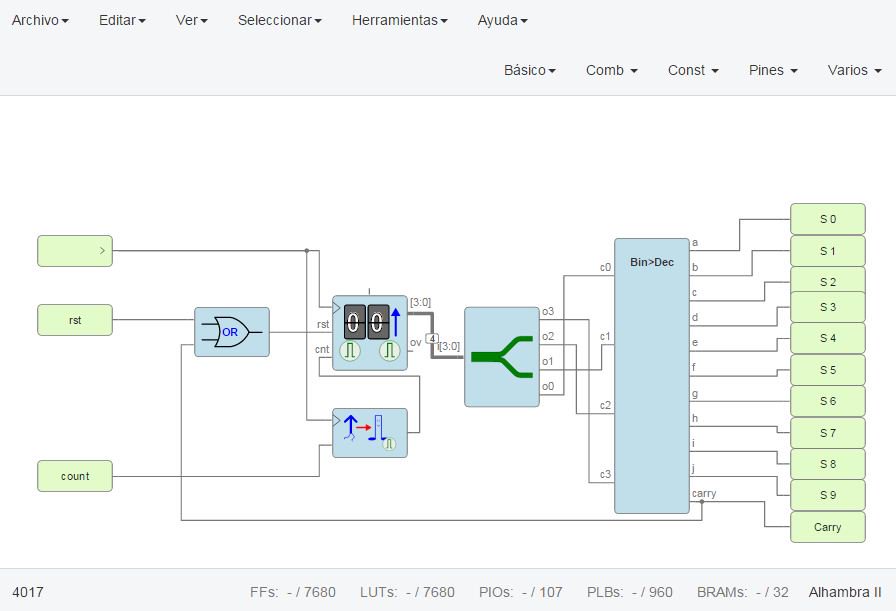

Con lo anterior he hecho un bloque llamado BIN>DEC que he integrado en el bloque del 4017, quedando tan limpio como puede verse en la siguiente imagen...

...La entrada COUNT va a un bloque detector de flanco de subida, cuya salida va a un contador binario de 4 bits. El detector de flanco es necesario porque en caso contrario la respuesta del contador puede ser extraña. Esto no ocurriría en un contador normal, pero debemos pensar que se trata de un FPGA en que muchos procesos se influyen y actualizan en paralelo.

El módulo contador tiene tres entradas y una salida. La entrada COUNT, la entrada reset RST y una entrada auxiliar que va al reloj del sistema, necesaria para el bucle interno de conteo que depende de la sentencia "always".

La salida es de 4 bits pero sale en forma de bus, un recurso de Verilog que permite simplificar las conexiones multihilos entre bloques. Naturalmente, al utilizar mi anterior bloque decodificador bin-dec, que precisa de las entradas de bits individuales, en esta salida colocaremos un bloque separador, que nos convierte de nuevo el bus en bits en paralelo...

El bloque OR, cuya salida va la RST, tiene dos entradas, una externa para poder efectuar dicho reset desde una señal exterior, y otra que viene de la salida 10 del contador que corresponde a demás a la salida "CARRY" para poder encadenar más bloques similares. Como nuestro bloque sólo debe poder contar de 0-9, la salida 10 provoca un reset interno que lo pone a 0.

...Y no hay mucho más. La verdad es que este entorno me gusta porque es como volver a los principios de la informática, a las capas más básicas de hardware y manejo de bits individuales, con lo cual se adquiere unas bases de las que carecen la mayoría de informáticos, y que luego sirven para comprender estamentos más complejos.

Saludos